## **General Description**

The MAX2980 powerline communication analog frontend (AFE) integrated circuit (IC) is a state-of-the-art CMOS device that delivers high performance and low cost. This highly integrated design combines an analogto-digital converter (ADC), digital-to-analog converter (DAC), signal conditioning, and line driver. The MAX2980 substantially reduces previously required system components, while compatible with third-party HomePlug® devices. This device interfaces with many companion Digital PHY ICs to provide a complete powerline communication solution.

The advanced design of the MAX2980 allows operation without external control, enabling simplified connection to a variety of HomePlug Digital PHY ICs. Additional power-reduction techniques can be employed through the use of various control signals.

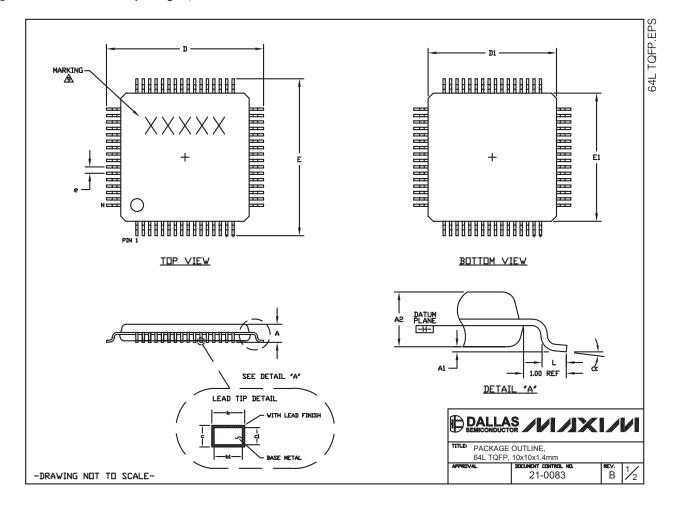

The MAX2980 is specified over the 0°C to +70°C commercial temperature range and is offered in a 64-pin TQFP package.

\_\_\_\_\_Applications

- Audio-Over-Powerline

- Voice-Over-Powerline

Security

- Remote Monitoring and Control

- Broadband Access (Last-Mile)

- Powerline-to-WiFi Bridge

- Powerline-to-DSL Bridge

- Powerline-to-Ethernet Bridge

- Powerline-to-USB Bridge

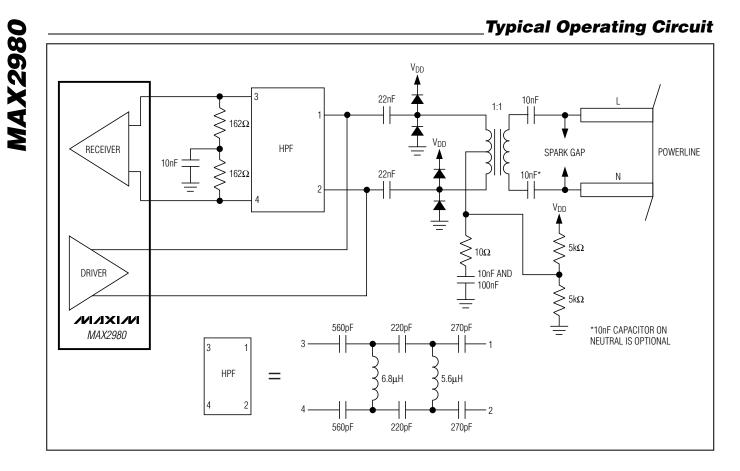

Typical Operating Circuit appears at end of data sheet.

HomePlug is a registered trademark of HomePlug Powerline Alliance, Inc.

# \_Features

- Fully Integrated Line Driver and Receiver

- Seamless Interface to Digital PHY ICs

- Fully Integrated 10-Bit ADC and DAC with 50MHz Sampling

- ♦ 54dB Adaptive Gain Control

- Minimum Line Impedance Capability as Low as 10  $\!\Omega$

- ♦ 3.0V to 3.6V I/O

- 250mA in Rx Mode and/or 160mA in Tx Mode at 3.3V

- ♦ 64-Pin TQFP Package

## **Ordering Information**

| PART       | TEMP RANGE   | PIN-PACKAGE |

|------------|--------------|-------------|

| MAX2980CCB | 0°C to +70°C | 64 TQFP     |

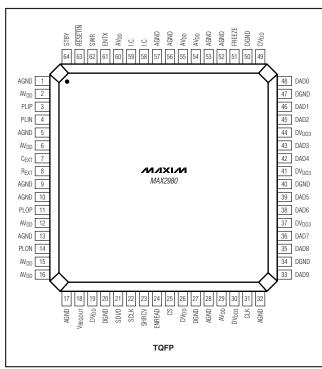

# Pin Configuration

# MAXIM

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

X 2980

### **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD</sub> to AGND                | 0.3V to +3.9V                    |

|-----------------------------------------|----------------------------------|

| DV <sub>DD3</sub> to DGND               | 0.3V to +3.9V                    |

| DV <sub>DD</sub> to DGND                | 0.3V to +2.8V                    |

| AGND to DGND                            | 0.3V to +0.3V                    |

| All Other Pins                          | 0.3V to (V <sub>DD</sub> + 0.3V) |

| Current into Any Pin                    | ±100mA                           |

| Short-Circuit Duration (VREGOUT to AGND | )10ms                            |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| 64-Pin TQFP (derate 25mW/°C above +70°                | C)2000mW       |

| Operating Temperature Range                           | 0°C to +70°C   |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 40°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**CAUTION!** ESD SENSITIVE DEVICE

## **ELECTRICAL CHARACTERISTICS**

$(AV_{DD} = DV_{DD3} = +3.3V, DV_{DD} = V_{REGOUT}, AGND = DGND = STBY = 0, T_A = 0°C to +70°C, unless otherwise noted. Typical values are at T_A = +25°C.)$

| PARAMETER                      | SYMBOL                                  |                   | CONDITION                          | 6                    | MIN | ТҮР | MAX | UNITS |  |

|--------------------------------|-----------------------------------------|-------------------|------------------------------------|----------------------|-----|-----|-----|-------|--|

| Operating Supply Voltage Range | AV <sub>DD</sub> ,<br>DV <sub>DD3</sub> | (Note 1)          |                                    |                      | 3.0 |     | 3.6 | V     |  |

|                                | DVDD                                    |                   |                                    |                      |     | 2.5 |     |       |  |

|                                |                                         | Receive           | Clock                              |                      |     | 250 |     |       |  |

|                                |                                         | mode              | No clock (Note 1)                  |                      | 175 | 220 | 260 |       |  |

|                                |                                         |                   | Newsel                             | Clock                |     | 250 |     |       |  |

| Quiescent Supply Current       | IDD                                     | Transmit          | Normal operation                   | No clock<br>(Note 1) | 175 | 220 | 260 | mA    |  |

|                                |                                         | mode              |                                    | Clock                |     | 160 |     |       |  |

|                                |                                         |                   | Receiver disabled,<br>SHRCV = high | No clock<br>(Note 1) | 100 | 135 | 165 |       |  |

|                                |                                         | Clock             | •                                  |                      |     | 20  |     |       |  |

| Standby Supply Current         |                                         | No clock (Note 1) |                                    |                      |     | 5   |     | mA    |  |

| Regulator Output               | VREGOUT                                 |                   |                                    |                      |     | 2.4 |     | V     |  |

| Output-Voltage High            | VOH                                     | (Note 1)          |                                    |                      | 2.4 |     |     | V     |  |

| Output-Voltage Low             | Vol                                     | (Note 1)          |                                    |                      |     |     | 0.4 | V     |  |

| LOGIC-INPUT CHARACTERISTIC     | s                                       |                   |                                    |                      |     |     |     |       |  |

| Input High Voltage             | VIH                                     |                   |                                    |                      | 2.0 |     |     | V     |  |

| Input Low Voltage              | VIL                                     |                   |                                    |                      |     |     | 0.8 | V     |  |

| Input Leakage Current High     | IIН                                     | VIH = VDI         | O(Note 1)                          |                      |     |     | +5  | μA    |  |

| Input Leakage Current Low      | ١ <sub>١L</sub>                         | VIL = 0 (N        | lote 1)                            |                      | -5  |     |     | μA    |  |

| ANALOG-TO-DIGITAL CONVERT      | ER (ADC) CI                             | ARACTE            | RISTICS                            |                      |     |     |     |       |  |

| Resolution                     | N                                       |                   |                                    |                      |     | 10  |     | Bits  |  |

| Integral Nonlinearity          | INL                                     |                   |                                    |                      |     | 2.1 |     | LSB   |  |

| Differential Nonlinearity      | DNL                                     |                   |                                    |                      |     | 0.4 |     | LSB   |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD3} = +3.3V, DV_{DD} = V_{REGOUT}, AGND = DGND = STBY = 0, T_A = 0^{\circ}C \text{ to } +70^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C.)$

| PARAMETER                            | SYMBOL           | CONDITIONS                                                              | MIN | ТҮР | MAX  | UNITS                 |

|--------------------------------------|------------------|-------------------------------------------------------------------------|-----|-----|------|-----------------------|

| DIGITAL-TO-ANALOG CONVERT            | ER (DAC) CI      | HARACTERISTICS                                                          |     |     |      |                       |

| Resolution                           | Ν                | 10                                                                      |     |     | Bits |                       |

| Integral Nonlinearity                | INL              |                                                                         |     | 0.4 |      | LSB                   |

| Differential Nonlinearity            | DNL              |                                                                         |     | 0.3 |      | LSB                   |

| Two-Tone Third-Order Distortion      | IM3              | Two tones at 17MHz and 18MHz, 1V <sub>P-P</sub> , differential          | 54  |     |      | dB                    |

| <b>RECEIVER CHARACTERISTICS</b>      |                  | · · ·                                                                   |     |     |      |                       |

| Common-Mode Voltage                  |                  | Pins PLIP/PLIN                                                          |     | 1.6 |      | V                     |

| Input Impedance per Pin              | ZIN              | Between pins PLIP, PLIN, and GND at 12 MHz                              |     | 875 |      | Ω                     |

| Two-Tone Third-Order Distortion      | IM3              | Two tones at 17MHz and 18MHz, 1V <sub>P-P</sub> , differential          |     | 53  |      | dB                    |

| AGC Gain Range                       | AGC              |                                                                         |     | 54  |      | dB                    |

| Lowpass-Filter Corner Frequency      |                  |                                                                         |     | 21  |      | MHz                   |

| Lowpass-Filter Ripple                |                  |                                                                         |     | 1.5 |      | dB                    |

| TRANSMITTER CHARACTERIST             | ICS              |                                                                         |     |     |      |                       |

| Common-Mode Voltage                  |                  | At pins PLOP/PLON                                                       |     | 1.6 |      | V                     |

| Output Impedance per Pin             | Z <sub>OUT</sub> | Between pins PLOP, PLON, and GND at 12MHz                               |     | 134 |      | Ω                     |

| Output-Voltage Swing at 12MHz        |                  | Predriver gain = -6dB                                                   |     | 2.4 |      | V <sub>P-P</sub> diff |

| Output-voltage Swing at 12MHz        |                  | Predriver gain = +3dB                                                   |     | 6.0 |      | vp-p uiii             |

| Short-Circuit Current                | Isc              |                                                                         |     | 230 |      | mA                    |

| Two-Tone Third-Order Distortion      | IM3              | Two tones at 17MHz and 18MHz, 1V <sub>P-P</sub> , differential (Note 1) | 35  | 50  | 70   | dB                    |

| Lowpass-Filter Corner Frequency      | T                |                                                                         |     | 21  |      | MHz                   |

| Lowpass-Filter Ripple                |                  |                                                                         |     | 1.5 |      | dB                    |

| Minimum Line Impedance<br>Capability |                  | <1dB output swing variation<br><1dB linearity variation                 |     | 10  |      | Ω                     |

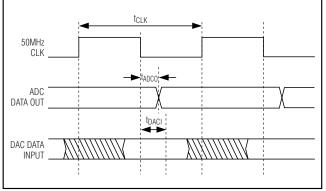

## TIMING CHARACTERISTICS

$(AV_{DD} = DV_{DD3} = +3.3V, DV_{DD} = V_{REGOUT}, AGND = DGND = STBY = 0, T_A = 0^{\circ}C$  to  $+70^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                 | SYMBOL        | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|-------------------------------------------|---------------|------------|-----|-----|-----|-------|

| CLK Frequency                             |               |            |     | 50  |     | MHz   |

| CLK Tolerance                             |               |            | -25 |     | +25 | ppm   |

| CLK Fall to ADC Data Output<br>Valid Time | tadco         |            |     | 2   |     | ns    |

| CLK Fall to DAC Data Latch Time           | <b>t</b> DACI |            |     | 3   |     | ns    |

**Note 1:** Guaranteed by production test at  $T_A = +27^{\circ}C$  and  $T_A = +70^{\circ}C$  and by design and characterization at  $T_A = 0^{\circ}C$ .

## **Pin Description**

| PIN                                               | NAME              | FUNCTION                                                                                                                                                                                                |

|---------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 5, 9, 10, 13,<br>17, 28, 32, 52,<br>53, 56, 57 | AGND              | Analog Ground                                                                                                                                                                                           |

| 2, 6, 12, 15, 16,<br>29, 54, 55, 60               | AV <sub>DD</sub>  | Analog Power-Supply Voltage. AV_{DD} supply range is 3.0V to 3.6V. Bypass AV_{DD} with a 0.1 $\mu F$ capacitor to AGND.                                                                                 |

| 3                                                 | PLIP              | AC Powerline Positive Input                                                                                                                                                                             |

| 4                                                 | PLIN              | AC Powerline Negative Input                                                                                                                                                                             |

| 7                                                 | C <sub>EXT</sub>  | External Capacitor Connection. Connect a 10nF capacitor from CSG to AGND.                                                                                                                               |

| 8                                                 | R <sub>EXT</sub>  | External Resistor Connection. Connect a $25k\Omega$ resistor from EXT to AGND.                                                                                                                          |

| 11                                                | PLOP              | AC Powerline Positive Output                                                                                                                                                                            |

| 14                                                | PLON              | AC Powerline Negative Output                                                                                                                                                                            |

| 18                                                | VREGOUT           | Voltage Regulator Output. Connect V <sub>REGOUT</sub> to DV <sub>DD</sub> for normal operation.                                                                                                         |

| 19, 26, 49                                        | DVDD              | Digital 2.5V Voltage Input. Connect to V <sub>REGOUT</sub> for normal operation.                                                                                                                        |

| 20, 27, 34, 40,<br>47, 50                         | DGND              | Digital Ground                                                                                                                                                                                          |

| 21                                                | SDI/O             | Serial Data Input and Output                                                                                                                                                                            |

| 22                                                | SCLK              | Serial Clock Input                                                                                                                                                                                      |

| 23                                                | SHRCV             | Receiver Shutdown Control. Drive SHRCV high to power down the receiver. Drive low for normal operation.                                                                                                 |

| 24                                                | ENREAD            | Read-Mode Enable Control. Drive ENREAD high to place the DAD [9:0] bidirectional buffers in read mode. Data are transferred from the Digital PHY to the AFE DAC. ENREAD signal frames the transmission. |

| 25                                                | CS                | Active-High Carrier-Select Input. Drive CS high to initiate the internal timer.                                                                                                                         |

| 30, 37, 41, 44                                    | DV <sub>DD3</sub> | Digital Power-Supply Voltage. $DV_{DD3}$ supply range is 3.0V to 3.6V. Bypass $DV_{DD3}$ to DGND with a 0.1µF capacitor as close to the pin as possible.                                                |

| 31                                                | CLK               | 50MHz System Clock Input                                                                                                                                                                                |

|                                                   |                   | ł                                                                                                                                                                                                       |

4

# \_Pin Description (continued)

| 33     | DAD9    | DAC/ADC Input/Output MSB Data Bit. Input/output of 10-bit, 50MHz bidirectional digital-to-analog and analog-to-digital converter. Data is in binary format.                           |

|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35     | DAD8    | DAC/ADC Input/Output Data Bit 8. Input/output of 10-bit, 50MHz bidirectional digital-to-analog and analog-to-digital converter. Data is in binary format.                             |

| 36     | DAD7    | DAC/ADC Input/Output Data Bit 7. Input/output of 10-bit, 50MHz bidirectional digital-to-analog and analog-to-digital converter. Data is in binary format.                             |

| 38     | DAD6    | DAC/ADC Input/Output Data Bit 6. Input/output of 10-bit, 50MHz bidirectional digital-to-analog and analog-to-digital converter. Data is in binary format.                             |

| 39     | DAD5    | DAC/ADC Input/Output Data Bit 5. Input/output of 10-bit, 50MHz bidirectional digital-to-analog and analog-to-digital converter. Data is in binary format.                             |

| 42     | DAD4    | DAC/ADC Input/Output Data Bit 4. Input/output of 10-bit, 50MHz bidirectional digital-to-analog and analog-to-digital converter. Data is in binary format.                             |

| 43     | DAD3    | DAC/ADC Input/Output Data Bit 3. Input/output of 10-bit, 50MHz bidirectional digital-to-analog and analog-to-digital converter. Data is in binary format.                             |

| 45     | DAD2    | DAC/ADC Input/Output Data Bit 2. Input/output of 10-bit, 50MHz bidirectional digital-to-analog and analog-to-digital converter. Data is in binary format.                             |

| 46     | DAD1    | DAC/ADC Input/Output Data Bit 1. Input/output of 10-bit, 50MHz bidirectional digital-to-analog and analog-to-digital converter. Data is in binary format.                             |

| 48     | DAD0    | DAC/ADC Input/Output LSB Data Bit. Input/output of 10-bit, 50MHz bidirectional digital-to-analog and analog-to-digital converter. Data is in binary format.                           |

| 51     | FREEZE  | Active-High Freeze-Mode Enable. Drive FREEZE high to place the AGC adaptation in freeze mode.<br>Drive FREEZE low if the the signal is not available for the companion baseband chip. |

| 58, 59 | I.C.    | Internally Connected. Leave these pins floating.                                                                                                                                      |

| 61     | ENTX    | Active-High Transmit Enable. Drive ENTX high to enable the transmitter. Drive ENTX low to place the transmitter in tri-state.                                                         |

| 62     | SWR     | Active-High Register Write Enable. Drive SWR high to place the registers in write mode.                                                                                               |

| 63     | RESETIN | Active-Low Reset Input. Drive RESETIN low to place the MAX2980 in reset mode. Set CLK in free-<br>running mode during a reset. The minimum reset pulse width is 100ns.                |

| 64     | STBY    | Active-High Standby Input. Drive STBY high to place the MAX2980 in standby mode. Drive low for normal operation.                                                                      |

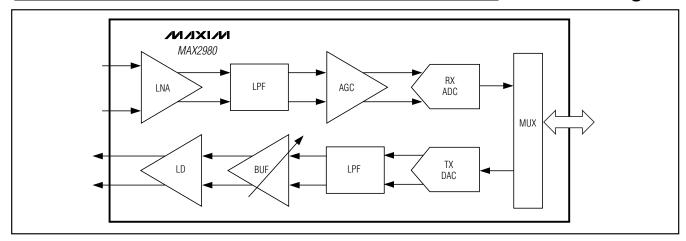

**Functional Diagram**

#### **Detailed Description**

The MAX2980 powerline communication AFE integrated circuit is a state-of-the-art CMOS device that delivers high performance and Iow cost. This highly integrated design combines the ADC, DAC, signal conditioning, and line driver as shown in the *Functional Diagram*. The MAX2980 substantially reduces previously required system components, while compatible to third-party HomePlug devices. This device interfaces with many companion Digital PHY ICs to provide a complete powerline communication solution.

The advanced design of the MAX2980 allows operation without external control, enabling simplified connection to third-party Digital PHY chips. Additional powerresource-management techniques can be employed in Rx and Tx modes through the use of various control signals.

#### **Receive Channel**

The receiver analog front-end consists of a low-noise amplifier (LNA), a lowpass filter (LPF), and an adaptive gain-control circuit (AGC). An ADC block samples the AGC output. The ADC communicates to the Digital PHY chip through a mux block.

The LNA reduces the receive channel input-referred noise by providing some signal gain to the AFE input.

The filter blocks remove unwanted noise, and provide the anti-aliasing required by the ADC for accurate sampling.

The AGC scales the signal for conversion from analog to digital. The scaling maintains the optimum signal level at the ADC input and keeps the AGC amplifiers out of saturation. The 50MHz, 10-bit ADC samples the analog signal and converts it to a 10-bit digital stream. The block fully integrates reference voltages and biasing for the input differential signal.

#### **Transmit Channel**

The transmit channel consists of a 10-bit digital-to-analog converter (DAC), a lowpass filter, and an adjustable gain transmitter buffer and line driver. The DAC receives the data stream from the Digital PHY IC through the mux block.

The 50MHz, 10-bit DAC provides the complementary function to the receive channel. The DAC converts the 10-bit digital stream to an analog voltage at a 50MHz rate.

The lowpass filter removes spurs and harmonics adjacent to the desired passband to help reduce the out-of- band transmitted frequencies and energy from the DAC output.

The transmit buffer and line-driver blocks allow the output level of the lowpass filter to obtain a level necessary to connect directly to the powerline medium, without the use of external amplifiers and buffers. The output level is adjustable between 2.4VP-P diff and 6.0VP-P diff. The line driver can drive resistive loads as low as  $10\Omega$ .

#### **Digital Interface**

The digital interface is composed of some control signals and a 10-bit bidirectional data bus for the DAC and ADC. The control signals include a reset line, a transmit request, an I/O detection request, and a receiver shutdown control.

# **Control Signals**

#### Transmit Enable (ENTX)

The ENTX line is used to enable the transmitter of the MAX2980 AFE circuit. With ENTX and ENREAD driven high, data sent to the DAC through DAD [9:0] is conditioned and delivered onto the power line.

#### Read Enable (ENREAD)

The ENREAD line sets the direction of the data bus DAD [9:0]. With ENREAD high, data is sent from the Digital PHY to the DAC in the MAX2980 AFE. A low on ENREAD sends data from the ADC to the Digital PHY.

#### **Receiver Power-Down (SHRCV)**

The SHRCV line provides receiver shutdown control. A logic-high on SHRCV powers down the receiver section of the MAX2980 whenever the device is transmitting. The MAX2980 also features a transmit power-saving mode, which reduces supply current from 410mA to 160mA. To enter the transmit power-saving mode, drive SHRCV high 0.1µs prior to the end of transmission. Connect SHRCV to ENTX and ENREAD for normal operation.

#### Digital-to-Analog and Analog-to-Digital Converter Input/Output (DAD [9:0])

DAD [9:0] is the 10-bit bidirectional bus connecting the Digital PHY to the MAX2980 DAC and ADC. The bus direction is controlled by ENREAD, as described in the *Read Enable* section.

#### AGC Control Signal (CS)

The CS signal controls the AGC circuit of the receive path in the MAX2980. A logic-low on CS sets the gain circuit on the input signal to continuously adapt for maximum sensitivity. A valid preamble detected by the Digital PHY raises CS to high. While CS is high, the AGC continues to adapt for an additional short duration, then it locks the currently adapted level on the incoming signal. The Digital PHY holds CS high while receiving a transmission, and then lowers CS for continuous adaptation for maximum sensitivity of other incoming signals.

#### AGC Freeze Mode (FREEZE)

Use the FREEZE signal to lock the AGC gain. Note if CS or FREEZE is not used, the maximum loss in SNR is 1dB due to modulation effects generated by the AGC circuit on some selective channels.

#### Clock (CLK)

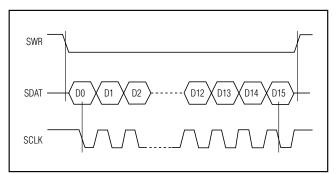

The CLK signal provides all timing for the MAX2980. Apply a 50MHz clock to this input. See the timing diagram of Figure 1 for more information.

Figure 1. ADC and DAC Timing Diagram

#### Reset Input (RESETIN)

MAX2980

The RESETIN signal provides reset control for the MAX2980. To perform a reset, set CLK in free-running mode and drive RESETIN low for a minimum of 100ns. Always perform a reset at power-up.

#### Standby Control (STBY)

The MAX2980 features a low-power, shutdown mode that is activated by STBY. Drive STBY high to place the MAX2980 in standby mode. In standby, the MAX2980 consumes only 20mA with a clock and 5mA without a clock.

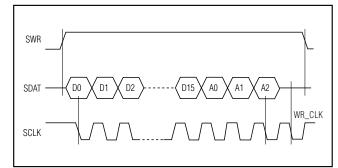

#### MAX2980 Control Registers

#### MAX2980 Serial Interface

The 3-wire serial interface controls the MAX2980 operation mode. The SCLK is the serial clock line for register programming. The SDI/O is the I/O serial data input and output for register writing or reading. The SWR signal controls WRITE/READ mode of the serial interface.

If SWR is high, the serial interface is in WRITE mode and a new value can be written into MAX2980 registers. Following SWR low-to-high transitions, data are shifted synchronously to (LSB first) registers on the falling edge of the serial clock (SCLK) as illustrated in Figure 2. Note that one extra clock (WR\_CLK) is required to write the content of holding the buffer to the appropriate register bank.

If SWR is low, the serial interface is in READ mode and the value of the current register can be read. The read operation to a specific register must be followed right after writing to the same register. Following SWR highto-low transitions, data are shifted synchronously to (LSB first) registers on the falling edge of the serial clock (SCLK) as illustrated in Figure 3.

The MAX2980 has a set of six READ/WRITE registers; bits A2, A1, A0 are the register address bits.

Figure 2. Writing Mode Register Timing Diagram

MAX2980

## Table 1. MAX2980 Registers Address

| REGISTER | A2 | A1 | A0 |

|----------|----|----|----|

| R1 (R/W) | 0  | 0  | 0  |

| R2 (R/W) | 0  | 0  | 1  |

| R3 (R/W) | 0  | 1  | 0  |

| R4 (R/W) | 0  | 1  | 1  |

| R5 (R/W) | 1  | 0  | 0  |

| R6 (R/W) | 1  | 0  | 1  |

#### MAX2980 AFE Register Maps

## Table 2. Register R1 Map

| REGISTER BIT NO. | DEFAULT | COMMENT                                                                                                       |

|------------------|---------|---------------------------------------------------------------------------------------------------------------|

| R1B0             | LOW     | Active high, powers down receiver when in transmit mode. Based on SHRCV signal going high (enable SMT1 mode). |

| R1B1             | HIGH    | Active high, powers down transmitter when in receive mode. Based on Tx signal going high (enables SMT2 mode). |

| R1B2             | LOW     | Active high, powers down DAC when in receive mode. Based on Tx signal going high (SMTDA mode).                |

| R1B3             | LOW     | Active high, powers down entire chip.                                                                         |

| R1B4             | LOW     | Reserved.                                                                                                     |

| R1B5             | LOW     | Reserved.                                                                                                     |

| R1B6             | LOW     | Reserved.                                                                                                     |

| R1B7             | LOW     | Reserved.                                                                                                     |

| R1B8             | LOW     | Reserved.                                                                                                     |

| R1B9             | LOW     | Reserved.                                                                                                     |

| R1B10            | LOW     | Reserved.                                                                                                     |

| R1B11            | LOW     | Reserved.                                                                                                     |

| R1B12            | LOW     | Reserved.                                                                                                     |

| R1B13            | LOW     | Reserved.                                                                                                     |

| R1B14            | LOW     | Reserved.                                                                                                     |

| R1B15            | LOW     | Reserved.                                                                                                     |

Note: Bits 4–15 control power-down on various blocks.

Figure 3. Reading Mode Register Timing Diagram

| REGISTER BIT NO. | DEFAULT | COMMENT                              |

|------------------|---------|--------------------------------------|

| R2B0             | LOW     | Reserved.                            |

| R2B1             | LOW     | Reserved.                            |

| R2B2             | LOW     | Reserved.                            |

| R2B3             | HIGH    | Reserved.                            |

| R2B4             | LOW     | Reserved.                            |

| R2B5             | LOW     | Reserved.                            |

| R2B6             | LOW     | Reserved.                            |

| R2B7             | LOW     | Reserved.                            |

| R2B8             | LOW     | Reserved.                            |

| R2B9             | LOW     | Reserved.                            |

| R2B10            | LOW     | Reserved.                            |

| R2B11            | LOW     | Reserved.                            |

| R2B12            | LOW     | Reserved.                            |

| R2B13            | LOW     | Reserved.                            |

| R2B14            | LOW     | Reserved.                            |

| R2B15            | LOW     | Active high, bypass the receive LPF. |

## Table 3. Register R2 Map

Note: Bit 0 to Bit 2 and Bits 4–14 must be set low to disable the connection to the test bus.

## Table 4. Register R3 Map

| REGISTER BIT NO. | DEFAULT | COMMENT                                                                                 |

|------------------|---------|-----------------------------------------------------------------------------------------|

| R3B0             | LOW     | Reserved.                                                                               |

| R3B1             | LOW     | neselveu.                                                                               |

| R3B2             | LOW     | These set the predriver gain as follows setting 000 to 111:                             |

| R3B3             | LOW     | 3dB, 2dB, 1dB, 0dB, -1dB, -2dB, -3dB, -6dB                                              |

| R3B4             | LOW     | R3B2 is the LSB.                                                                        |

| R3B5             | LOW     |                                                                                         |

| R3B6             | LOW     |                                                                                         |

| R3B7             | LOW     | Perenved                                                                                |

| R3B8             | LOW     | Reserved.                                                                               |

| R3B9             | LOW     |                                                                                         |

| R3B10            | LOW     |                                                                                         |

| R3B11            | HIGH    | Active high, place process tune in continuous mode. Otherwise active only during RESET. |

| R3B [15:12]      | 0111    | Reserved.                                                                               |

# **MAX2980**

## Table 5. Register R4 Map

| REGISTER BIT NO. | DEFAULT | COMMENT   |

|------------------|---------|-----------|

| R4B0             | LOW     | Reserved. |

| R4B1             | HIGH    | Reserved. |

| R4B2             | HIGH    | Reserved. |

| R4B3             | HIGH    | Reserved. |

| R4B4             | LOW     | Reserved. |

| R4B5             | LOW     | Reserved. |

| R4B [10:6]       | 01011   | Reserved. |

| R4B11            | HIGH    | Reserved. |

| R4B12            | HIGH    | Reserved. |

| R4B13            | HIGH    | Reserved. |

| R4B14            | HIGH    |           |

| R4B15            | LOW     | Reserved. |

## Table 6. Register R5 Map

| REGISTER BIT NO. | DEFAULT | COMMENT                                                                                     |

|------------------|---------|---------------------------------------------------------------------------------------------|

| R5B [6:0]        | LOW     |                                                                                             |

| R5B [12:7]       | LOW     |                                                                                             |

| R5B13            | LOW     | Set to manually control VGA and offset-cancellation circuits. Low for automatic adaptation. |

| R5B14            | LOW     |                                                                                             |

| R5B15            | LOW     |                                                                                             |

# Applications Information

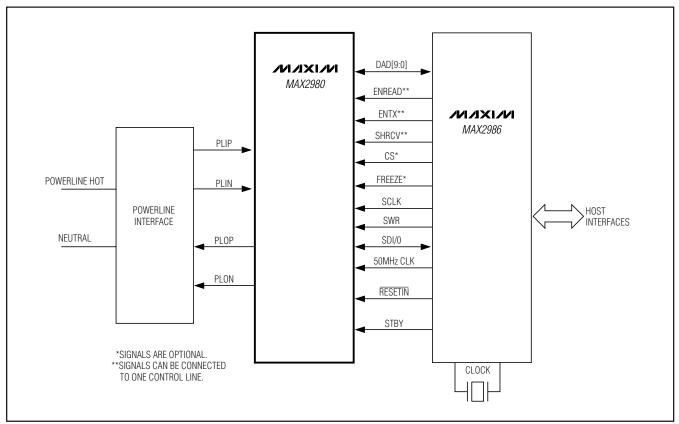

#### Interfacing to Digital PHY Circuit

The MAX2980 interfaces to the MAX2986 Digital PHY IC using a bidirectional bus to pass the digital data to and from the DAC and ADC. Handshake lines help accomplish the data transfer and operation of the MAX2980. The application circuit diagram of Figure 4 shows the connection of the MAX2980 to the MAX2986 digital baseband chip.

#### **Layout Considerations**

A properly designed PC board is an essential part of any high-speed circuit. Use controlled-impedance lines on all frequency inputs and outputs. Use low-inductance connections to ground on all ground pins and wherever the components are connected to ground. Place decoupling capacitors close to all V<sub>DD</sub> connections. For proper operation, connect the metal exposed paddle at the back of the IC to the PC board ground plane with multiple vias.

## Table 7. Register R6 Map

| REGISTER BIT NO. | DEFAULT | COMMENT                                    |

|------------------|---------|--------------------------------------------|

| R6B0             | LOW     | Reserved.                                  |

| R6B [2:1]        | 00      | Reserved.                                  |

| R6B3             | LOW     | Reserved.                                  |

| R6B4             | LOW     | Active high, allow BYPASS of transmit LPF. |

| R6B [6:5]        | 00      |                                            |

| R6B7             | LOW     |                                            |

| R6B8             | LOW     |                                            |

| R6B9             | LOW     | Pesserved                                  |

| R6B [11:10]      | 10      | Reserved.                                  |

| R6B [13:12]      | 00      |                                            |

| R6B14            | HIGH    |                                            |

| R6B15            | HIGH    |                                            |

Figure 4. Interfacing the MAX2980 to the MAX2986

11

**MAX2980**

\_Chip Information

TRANSISTOR COUNT: 64,841 PROCESS: CMOS

## \_Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

## **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

#### NDTES:

- 1. ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5-1982.

- DATUM PLANE [H] IS LICATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION IS 0.25 MM ON D1 AND E1 DIMENSIONS D1

- DIMENSIONS. THE TOP OF PACKAGE IS SMALLER THAN THE BOTTOM OF PACKAGE BY 0.15 MILLIMETERS.

- 5. DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 MM TOTAL IN EXCESS OF THE 6 DIMENSION AT MAXIMUM MATERIAL CONDITION. 6. ALL DIMENSIONS ARE IN MILLIMETERS.

- 7. THIS DUTLINE CONFORMS TO JEDEC PUBLICATION 95, REGISTRATION MS-026, VARIATION BCD.

- LEADS SHALL BE COPLANAR WITHIN .004 INCH.

- 8. LEADS SHALL BE CUPLANAR WITHIN JUN AND AND THE AND A STATE AND

| J   | EDEC VAR  | IATION |  |  |

|-----|-----------|--------|--|--|

|     | BCD       |        |  |  |

|     | 64 L      | EAD    |  |  |

|     | MIN.      | MAX.   |  |  |

| A   |           | 1.60   |  |  |

| A1  | 0.05      | 0.15   |  |  |

| Aa  | 1.35      | 1.45   |  |  |

| D   | 11.80     | 12.20  |  |  |

| D1  | 9.80      | 10.20  |  |  |

| Е   | 11.80     | 12.20  |  |  |

| E1  | 9.80      | 10.20  |  |  |

| e   | 0.50 BSC. |        |  |  |

| L   | 0.45      | 0.75   |  |  |

| ю   | 0.17      | 0.27   |  |  |

| lo1 | 0.17      | 0.23   |  |  |

| с   | 0.09      | 0.20   |  |  |

| c1  | 0.09      | 0.16   |  |  |

| α   | 0.        | 7°     |  |  |

|                        |                      | \$ <i>/</i> И/JX        |   | M   |

|------------------------|----------------------|-------------------------|---|-----|

|                        | PACKAGE<br>64L TQFP, | OUTLINE,<br>10x10x1.4mm |   |     |

| -DRAWING NOT TO SCALE- | APPROVAL             | 21-0083                 | B | 2/2 |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2005 Maxim Integrated Products Printed USA **MAXIM** is a registered trademark of Maxim Integrated Products, Inc.